## BINDURA UNIVERSITY OF SCIENCE EDUCATION PHYSICS AND ENGINEERING DEPARTMENT PH115: DIGITAL LOGIC EXAMINATION DURATION: 3 HOURS

- JUN 2025

Answer ALL questions in Section A and any THREE questions from Section B. Section A carries 40 marks and each question in Section B carries 20 marks.

## **SECTION A** (Answer ALL the questions in this section)

| <ol> <li>(a) (i) Draw the electronic symbol for an AND gate.</li> <li>(ii) Construct a truth table for the AND gate.</li> </ol>                                          | [3]<br>[5]  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| (b) With the aid of a truth table and a diagram, briefly explain how an OR gate can be used to design an electronic gate lock that needs two separate keys to unlock it. | )<br>[10]   |

| (c) What is the name of the gate that is often called an inverter? Explain your answer.                                                                                  | [4]         |

| (d) Use two switches, an LED and a dc power supply to draw a circuit diagram who behaves in exactly the same way as an OR gate. Explain your diagram.                    | nich<br>[6] |

| (e) Using NAND gates only, show how you can implement the EX-OR gate. Hence, draw a truth table for the EX-OR gate.                                                      | [12]        |

## **SECTION B** (Answer **THREE** questions from this section)

2. A logic circuit with two inputs X and Y and output Q has the following the Boolean equation:

$$Q = \left(\overline{X} + \overline{Y}\right) \bullet \left(X + Y\right)$$

(a) Copy and complete Table 2.1.

[10]

Table 2.1: Truth table.

| X | Υ | $\overline{X}$ | $\overline{Y}$ | $\overline{X} + \overline{Y}$ | X + Y | Q |

|---|---|----------------|----------------|-------------------------------|-------|---|

| 0 | 0 |                |                |                               |       |   |

| 1 | 0 |                |                |                               |       |   |

| 0 | 1 |                |                |                               |       |   |

| 1 | 1 |                |                |                               |       | , |

(b) Complete Figure 2.1 to show how a logic circuit can be constructed from two NOT gates, two OR gates and one AND gate to represent the Boolean equation above.

**X**  $\circ$ ——

——○ **Q**

YO

Figure 2.1: Part of a logic circuit.

- (c) Which single logic gate has the same function as the complete circuit above? [1]

- 3. (a) What is a logic gate? [2]

- (b) With the aid of a truth table, briefly describe how you can make a NOT gate from:

- (i) a NAND gate, and

[7]

(ii) a NOR gate.

[7] -

- (c) State with an explanation, the other name for:

- (i) the EX-OR gate,

[2]

(ii) the EX-NOR gate.

[2]

4. (a) What is a truth table? [2]

(b) Figure 4.1 shows a logic gate.

Figure 4.1: A logic gate.

- (i) What name do we give to this type of gate?

(ii) Construct its truth table.

[9]

- (iii) Explain why the logic gate shown in Figure 4.1 is referred to as the parity gate. [2]

- (c) Table 4.1 shows how the input sensors A and B of an electronic system control the outputs P, Q and R.

Table 4.1: The truth table showing how the input sensors control the output.

| A | В | Р | Q | R |

|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

- (i) Which type of logic gate will produce the P output?

(ii) Which type of logic gate will produce the Q output?

(iii) Write down an expression which describes the R output.

[2]

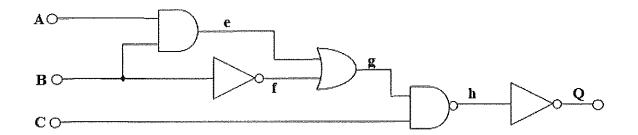

- **5.** Figure 5.1 shows a logic circuit with three inputs (i.e.), A, B and C.

Figure 5.1: Logic gate combinations.

Construct a truth table for this logic gate network.

[20]

6. The truth table for a logic circuit is shown Table 6.1.

Table 6.1: Truth table.

| W | Х | Υ | Z | Q |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 |

(a) Inputs W and X are connected to two logic gates having outputs Y and Z.

Given that Y and Z form the inputs to a third gate which provides the output Q. Complete Figure 6.1 by drawing the logic circuit that would give these outputs.

[12]

**W** 🖰 \_\_\_\_\_

——○ **Q**

X ().....

Z

Figure 6.1: Part of a logic circuit.

(b) Use Table 6.1 to write the simplest Boolean expression for the logic signals

|     | at Y and Z in terms of the inputs W and X.                                                                               | [4] |

|-----|--------------------------------------------------------------------------------------------------------------------------|-----|

| (c) | Write the simplest Boolean expression for $\boldsymbol{Q}$ in terms of the inputs $\boldsymbol{W}$ and $\boldsymbol{X}.$ | [3] |

| (d) | Name a single logic gate which performs the same function as the complete                                                |     |

|     | circuit above.                                                                                                           | [1] |

## END OF PAPER