# BINDURA UNIVERSITY OF SCIENCE EDUCATION FACULTY OF SCIENCE AND ENGINEERING DEPARTMENT COMPUTER SCIENCE BSc HONS DEGREE IN COMPUTER SCIENCE DEGREE/INFORMATION TECHNOLOGY

COURSE CODE CS113/NWE114/SWE203: COMPUTER ARCHITECTURE

**DURATION: 2 HOURS 30 MINUTES**

**TOTAL MARKS: 100**

### **INSTRUCTIONS TO CANDIDATES**

This paper contains five questions Answer all questions.

, = MON 2024

## Question 1

- a) In a von Neumann architecture, we use a program counter (PC) to indicate the address of the instruction to be executed next. After this instruction is fetched, the program counter increases its stored value by 1, indicating that the next instruction to be executed is usually the one stored in the following memory address. Sometimes, however, the address stored in the PC will be changed during the execution of the current instruction. Why? Please give two scenarios to show the change of the PC value to something else than the previous value plus 1. Use a concrete example to illustrate each of these two scenarios. [8]

- b) How much memory (in Kilobytes) is addressable in the intel 8085 and 8086 microprocessors given that the intel 8085 has a 16-bit address bus and the intel 8086 has a 20-bit address bus.

### Question 2

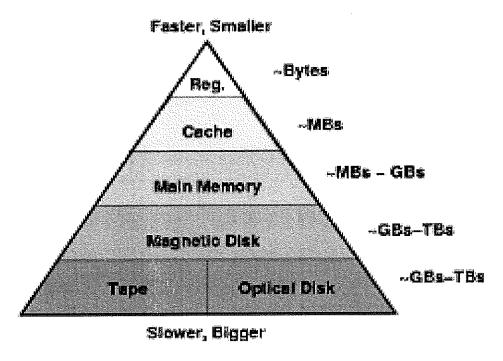

a) Explain the difference between internal computer memory and external computer memory.

b) The following diagram summarizes the concept of hierarchical computer memory organization. Discuss each of the components and explain why the diagram in fig 1 has a pyramidal shape. [12]

Figure 1: Memory hierarchy

- c) Explain the justification for hierarchical memory organization. [4]

- d) Modify the diagram to demonstrate the influence of cloud computing in hierarchical memory organization and give a brief explanation. [6]

# Question 3

- a) What is a pipeline hazard in an instruction pipeline? [2]

- b) In your opinion, which pipeline hazard causes the biggest problem for instruction pipeline? Why?

- c) In general, a larger number of pipeline stages gives a better performance. However, this has not led to the situation that we have a huge number of pipeline stages. Why?

[4]

d) Identify all the different types of data dependencies in the following code. Indicate

the type of dependency you have identified for each one, and give the reasons for

your answers.

```

L1: add r3,r4,#4

store r8,(r3)

sub r8,r5,#4

load r9,(r8)

blt r9,r1,L1

Note: r3 := r4 + 4

Note: memory location pointed by r3 := r8

Note: r8 := r5 - 4

Note: r9 := memory location pointed by r8

Note: branch to L1 if r9 < r1

```

e) How can this penalty be reduced with the forwarding (bypassing) technique? Draw figures to illustrate the pipelined executions without and with forwarding. [6]

# Question 4

- a) Describe <u>three</u> features of RISC computers that you consider as the most important ones for performance improvement. For each feature, describe how it improves the performance of a computer.

- b) The designers of processor X decide to include some extra instructions to support multi-media applications, and with a rare touch of marketing genius, the code-name this new processor Y.

The table 1 shows comparative measurements of the CPI and the instruction counts (millions of instructions) for X and Y running the designer's favourite benchmark. These measurements are reported separately for six major groups of instructions (loads, stores, integer ALU operations, floating-point operations, branches and the new set of multimedia instructions).

| Instruction    | Class | Instructions executed $(\times 10^6)$ |      |

|----------------|-------|---------------------------------------|------|

| class          | CPI   | on X                                  | on Y |

| loads          | 1.2   | 25                                    | 25.  |

| stores         | 1.0   | 10                                    | 10   |

| int ALU        | 1.0   | 40                                    | 25   |

| floating-point | 3.6   | 5                                     | 5    |

| branches       | 1.1   | 20                                    | 18   |

| multi-media    | 1.0   | ()                                    | 4    |

Table 1: Instruction classes CPI

- i) Explain what is meant by a CPI measurement in the context of high performance processor architecture. [2]

- ii) What are the overall CPI values for X and Y, when running this benchmark?

- iii) What is the speedup or slowdown introduced by the new multi-media instructions? [2]

# Question 5

- a) A prime number is a number which is only divisible by only 1 and the number itself. To check whether a given number N is prime or not, we have to check if number is divisible by any number from 2 to N-1. If it is not divided by any number, then it is a prime number otherwise it is not a prime number. Write a MIPS assembly program to determine whether a given number from the keyboard is a prime number or not.

- b) Describe the two most suitable I/O techniques that could be used for transferring characters from a keyboard to the computer, giving advantages and a disadvantages for each.

[8]

#### **END OF PAPER**